虽然Haswell在大大小小的新闻、爆料中出场多次,但是系统性的资料还是凤毛麟角,我们只能从先前的报道中追踪Haswell架构中那些将会改变或者继承的设计。

CHH网友Bigpao007曝光过一份Haswell处理器的文档

综合性最强的资料还是先前CHH网友Bigpao007爆出的一组Haswell PDF资料,从中我们可以一窥Haswell秘境。

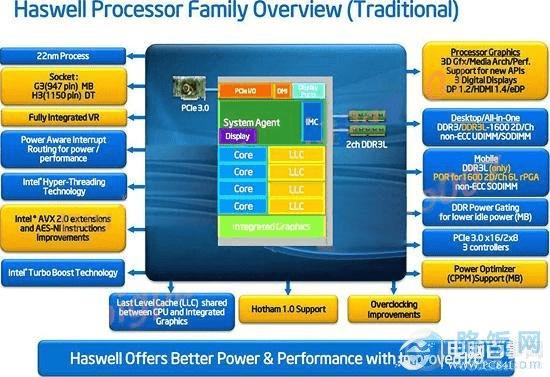

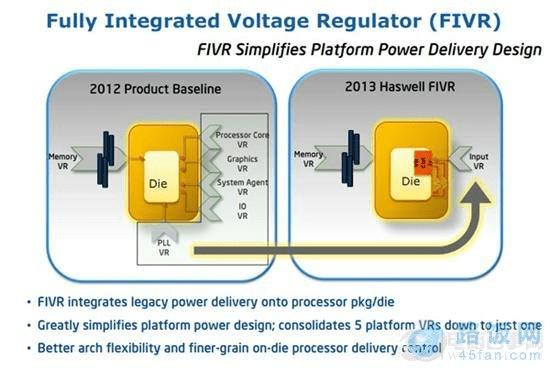

先来看改变的地方,首先是封装方式变了,移动平台将使用Socket G3插槽,947针脚,而桌面平台使用Socket H3插槽,1150针脚。第二则是指令集变化了,支持TSX扩展指令、AVX 2.0,这部分后面还要分别讲述。第三就是集成性更高,原来五部分的VR调压模块现在整合为一个。

原来的调压模块有Core、显卡、SA、I/O、PLL之分,现在统一为输入VR

不变的地方似乎更多,四核心八线程设计、Turbo加速、PCI-E 3.0、双通道DDR3/DDR3L内存支持等技术与目前的SNB、IVB架构基本相同。

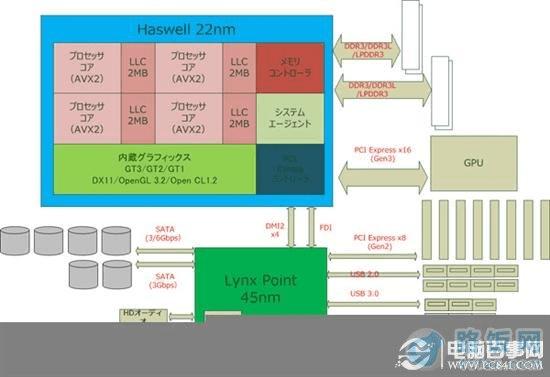

日本PCwatch网站曾专门介绍过Haswell的架构设计,这也是目前比较全面的Haswell架构图,官方版的还没见到过。

在这份图表上可以看到Haswell继续为长方形封装,内部集成4个核心,共享8MB L3缓存。CPU核心之外占用面积最大的就是新一代图形核心了,支持DX11.1、OpenGL 3.2以及OpenCL 1.2标准。

南桥方面则是代号Lynx Point的芯片组,最大特点是使用45nm工艺生产,相比目前65nm工艺的6系和7系主板来说更省电。

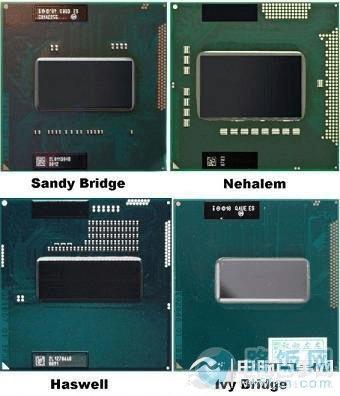

CPU架构方面可用资料不多,从先前报道过的各种晶圆核心来看,因为同为22nm工艺,其核心面积与目前的Ivy Bridge基本相同,但是晶体管数量之类的消息就无从得知了。

Haswell内核上变化最大的是指令集,一个是针对多线程应用的TSX扩展指令,来一个是就是现有AVX指令的进阶版AVX 2.0,它们对Haswell的性能提升至关重要,如果没有这两点,Haswell相对于IVB还真没什么重要升级可言了。

多线程助推剂 Haswell将支持TSX指令扩展

多线程多核处理器问世几年来,在AMD和Intel的轮番推动下双核、双核四线程CPU已经是最基本的配置,四核以及四核八线程也不是少数人的玩物了,总之就是多线程在物理基础上已经普及,但是日常应用中八线程并不能总是比双线程要快。

其中的原因有软件/游戏开发商对多核优化不够造成的,但是CPU自身也存在一定限制,比如传统操作中一个线程访问了某部分内存数据之后就会通过一个“lock”锁操作来保证数据的统一性,又分出粗粒度锁定(Coarse-grained thread lock)以及细粒度锁定(Fine-grained thread lock),无论是哪种锁都存在多线程并行的效率问题,因为锁操作是互斥的。

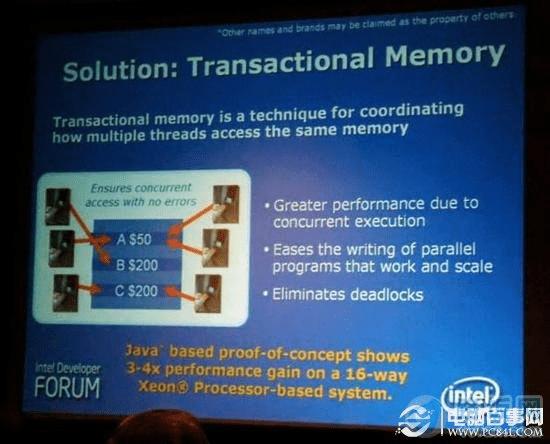

Intel早在2006年的IDF上就公布了这一问题的解决方案,那就是改用Transactional Memory(事务型内存),这一技术早在服务器处理器上应用多年,但在桌面CPU中还没有应用过,要等到Haswell这一代才能有实际应用。

Intel早前在其官方Blog上发表了一篇名为“Transactional Synchronization in Haswell”的文章,介绍了Haswell架构将会支持TSX扩展指令,简单来说就是TSX将允许程序员指定事务型同步代码空间,使得目前使用粗粒度线程锁定的程序更自由地使用细粒度线程锁定,进而提高多线程效率和性能。

举个简单的例子,你在编辑excel表格,如果你打算同时编辑两份拷贝,excel就会提示你该文件正在编辑,只能以只读方式打开但不能编辑,这种情况叫做粗粒度线程锁定,这种锁定比较简单,很容易实现,但是效率不高。

细粒度线程锁定则可以实现自由度更高的数据同步,还是前面的例子,如果使用细粒度线程锁定,那么每个线程都可以操作不同纵列的数据,明显提高了CPU效率,不过这样做也有更大的风险,比如数据出错的几率更大,特别是多个线程同时向一个区域写入数据时,而粗粒度线程锁定则可以避免这个问题,同时保持不需要的核心处于休眠状态,更节能。

为了避免出错,程序员往往钟爱粗粒度线程锁定,而TSX扩展的设计目的就是评估软硬件状况并为程序员提供无错的细粒度线程锁定。

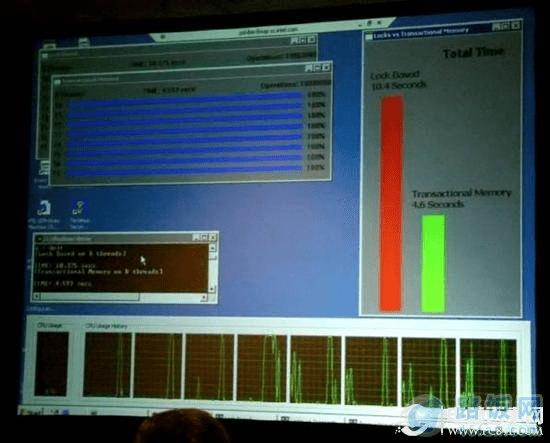

Intel在当时的软件仿真演示中表示使用事务内存技术后性能可以提升1-3倍,比如基于锁操作的测试需要10.4秒,而使用事务内存处理只需要4.6秒,性能是前者的2倍还多。

Haswell将是消费级处理器中首次使用事务内存技术的架构,虽然Intel已经展示了该技术的良好前景,特别是在复杂的多线程应用中其理应有更好的表现,不过回到现实中这一技术还需要系统在内存管理和线程调度上做相应的优化,具体性能提升只能拭目以待。

本文地址:http://www.45fan.com/dnjc/8535.html